FII-PRX100 Risc-V FPGA Board is a ready-to-use development platform designed around the Field Programmable Gate Array (FPGA) from Xilinx.

Open Source[edit]

There are many open-sourced RISC-V CPU designs, including:

- The Berkeley CPUs. These are implemented in a unique hardware design language, Chisel, and some are named for famous train engines:

- 64-bit Rocket. Rocket may suit compact, low-power intermediate computers such as personal devices. Named for Stephenson’s Rocket.

- The 64-bit Berkeley Out of Order Machine (BOOM). BOOM uses much of the infrastructure created for Rocket, and may be usable for personal, supercomputer, and warehouse-scale computers.

- Five 32-bit Sodor CPU designs from Berkeley, designed for student projects. Sodor is the fictional island of trains in childrens’ stories about Thomas the Tank Engine.

- picorv32 by Claire Wolf, a 32-bit microcontroller unit (MCU) class RV32IMC implementation in Verilog.

- scr1 from Syntacore,a 32-bit microcontroller unit (MCU) class RV32IMC implementation in Verilog.

- PULPino (Riscy and Zero-Riscy) from ETH Zürich / University of Bologna. The cores in PULPino implement a simple RV32IMC ISA for micro-controllers (Zero-Riscy) or a more powerful RV32IMFC ISA with custom DSP extensions for embedded signal processing.

It was designed to cover all aspects of FPGA Development and Experiment, RISC-V SOC .

The main application areas aim at smart home, Wearable, sensor Fusion, IOT, and industrial control etc.

FII-PRX100 Risc-V FPGA Board is a ready-to-use development platform designed around the Field Programmable Gate Array (FPGA) from Xilinx. It was designed to cover all aspects of FPGA Development and Experiment, RISC-V SOC . The main application areas aim at smart home, Wearable, sensor Fusion, IOT, and industrial control etc.

Features:

|

|

FII-PRX100 RISC-V development board

-

-

- Suitable for FPGA study and training

- Fully support FIE310 CPU running and system development

- Suitable for user customized RV32G verification and validation

- JTAG interface for FPGA and FIE310 CPU download and debug

- Support Windows software and linux development environment

- GCC compilation toolchain and graphical software development environment

- Hardware resource: Switchs, Push Button ,USB to UART convertor, QSPI flash, I2CEEPROM, 100M/1G ethernet,USB keyboard mouse,GPIO, hdmi transmitter and camera etc.

-

1.System Design Objective

The main purpose of this system design is to complete FPGA learning, development and experiment with Xilinx-Vivado. The main device uses the Xilinx-XC7A100T-2FGG676I and is currently the latest generation of FPGA devices from Xilinx. The main learning and development projects can be completed as follows:

-

-

- Basic FPGA design training

- Construction and training of the SOPC (Microblaze) system

- IC design and verification, the system provides hardware design, simulation and verification of RISC-V CPU

- Development and application based on RISC-V

- The system is specifically optimized for hardware design for RISC-V system applications.

-

2.System Resource

-

-

- Extended memory

- Use two Super Srams in parallel to form a 32-bit data interface with a maximum access space of 1M bytes.

- IS61WV25616 (2 pieces) 256K x 32bit

- Serial flash

- Spi interface serial flash (128M bytes)

- Serial EEPROM

- Gigabit Ethernet: 100/1000 Mbps

- USB to serial interface: USB-UART bridge

-

3.Human-computer Interaction Interface

-

-

- 8 toggle switches

- 8 push buttons

- Definition of 7 push buttons: up, down, left, right, ok, menu, return

- 1 for rest: Reset button

- 8 LEDs

- 6 7-segment decoders

- I2C bus interface

- UART external interface

- JTAG programming interfaces

- Integrated FPGA Jtag and Risc-V Jtag by using single USB port.

- Built-in RISC-V IPCore

- CPU software debugger, no external RISC-V JTAG emulator required

- 12-pin GPIO connectors, in line with PMOD interface compatible.

-

4 Software Development System

-

- Vivado 18.1 and later version for FPGA development, Microblaze SOPC

- Freedom Studio-Win_x86_64 Software development for RISC-V CPU

5. Supporting Resources

-

- RISC-V JTAG Debugger

- Xilinx Altera JTAG Download Debugger

- FII-PRX100 Development Guide

What is RISC-V Foundation?

RISC-V is a free and open ISA enabling a new era of processor innovation through open standard collaboration.

The RISC- V Foundation is a non-profit entity serving members and the industry and was originally developed in the Computer Science Division of the EECS Department at the University of California, Berkeley.

Recently RISC-V and GigaDevice announced the GD32V Series, which is said to be the world’s first 32-bit general-purpose microcontroller based on the RISC-V core.

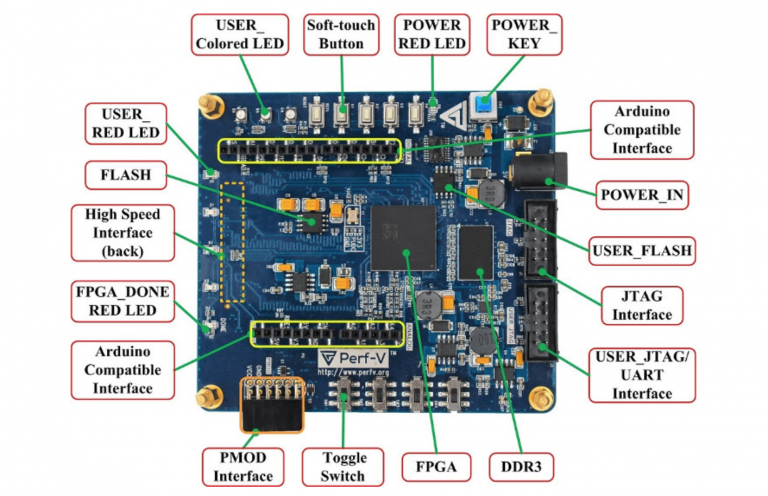

Perf-V is a FPGA demo board designed for RISC-V opensource community by PerfXLab. It integrates various peripheral chips and offers many interfaces.

- It uses Xilinx Artix-7 FPGA, Vivado software development,and is designed for the RISC-V open source community and FPGA learning enthusiasts design development board.

- It Integrates a variety of peripheral chips to provide a rich set of peripheral interfaces, including PMOD, Arduino, JTAG, UART interfaces, and high-speed interfaces for expansion of HDMI, VGA, USB2.0/3.0, camera, Bluetooth, expansion boards, etc. Strong flexibility.

- Based on Perf-V’s self-developed smart car, it can use mobile phone Bluetooth to control the movement of the car, and can realize automatic tracing and obstacle avoidance functions.

You can also choose another one with the chip XC7A100T-1FTG256C, which has more logic cells and CLBs.

What is the next board are you expecting? Please feel to let us know in the forum: New Product Ideas. We will carefully listen to and take action!