Codasip’s RISC-V-based processors (Bk) make use of the rich ecosystem of software and hardware enabled by the extensible, RISC-V Instruction-Set Architecture (ISA) Standard, while retaining the incredible flexibility of all Codasip-made cores.

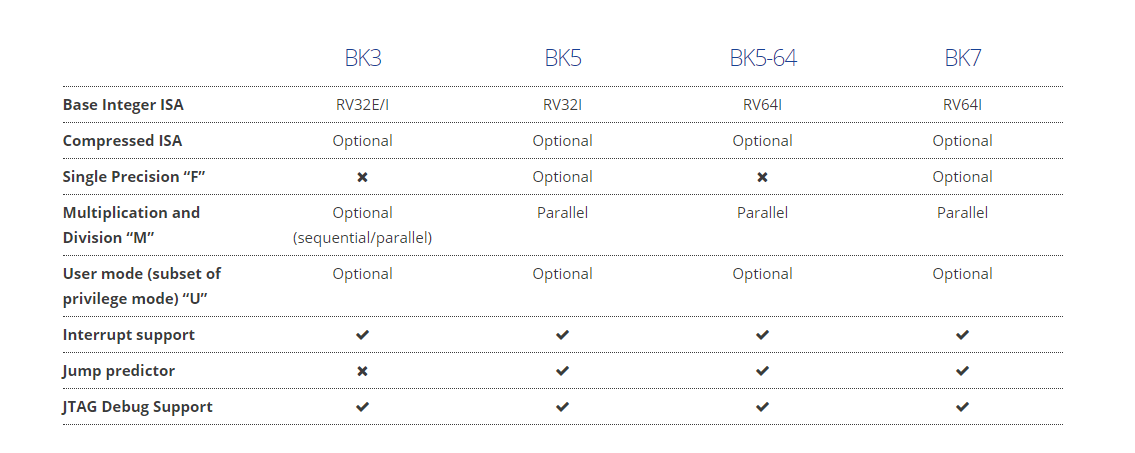

Codasip currently offers the following base versions of the RISC-V architecture: with a 3-stage, 5-stage, and a 7-stage pipeline. All are fully compliant with the RISC-V specification and fully customizable.

In addition to the base processor implementation, Codasip provides standard support for optional instruction layers as defined by the current RISC-V specification.

ll Codasip Bk cores are fully customizable to the needs of your design. Changes can be made by Codasip as part of the standard deliverable, or by your own developers using our unique IP Generation Toolkit (Codasip Studio).

Need a single-cycle MAC, specialized crypto functions, or support for non-standard data types? No problem. Better yet, thanks to the extensible nature of the RISC-V ISA, all tailored cores remain RISC-V compliant, allowing you to use the growing SW Ecosystem.

STATE-OF-THE-ART COMMERCIAL SDK SUPPORT

The Bk cores are supported by industry-leading SDK that is based on LLVM, GNU and other open standards, but is optimized for your unique processor configuration and backed by Codasip’s comprehensive support.

OPEN, EXTENSIBLE, INDUSTRY-SUPPORTED

Codasip is proud to be a founding member of the RISC-V Foundation, joining industry leaders such as Google, Oracle, HP, AMD, Nvidia, and many others.

The power of RISC-V board is that it defines an ISA that helps a healthy HW and SW ecosystems develop, allowing each vendor to deliver their own unique value.

Cloud server will use Risc-V Processor in the near future. If you want to have a cheap cloud hosting with no downtime, please go to PowerHoster.